## **Hands-On Electronics**

A Practical Introduction to Analog and Digital Circuits

Daniel M. Kaplan and Christopher G. White

This page intentionally left blank

#### **Hands-On Electronics**

Packed full of real circuits to build and test, *Hands-On Electronics* is a unique introduction to analog and digital electronics theory and practice. Ideal both as a college textbook and for self-study, the friendly style, clear illustrations and construction details included in the book encourage rapid and effective learning of analog and digital circuit design theory. All the major topics for a typical one-semester course are covered, including *RC* circuits, diodes, transistors, op amps, oscillators, digital logic, counters, D/A converters and more. There are also chapters explaining how to use the equipment needed for the examples (oscilloscope, multimeter and breadboard), together with pinout diagrams for all the key components referred to in the book.

## **Hands-On Electronics**

# A One-Semester Course for Class Instruction or Self-Study

Daniel M. Kaplan

and

Christopher G. White

Illinois Institute of Technology

CAMBRIDGE UNIVERSITY PRESS

Cambridge, New York, Melbourne, Madrid, Cape Town, Singapore, São Paulo

Cambridge University Press

The Edinburgh Building, Cambridge CB2 2RU, United Kingdom

Published in the United States of America by Cambridge University Press, New York www.cambridge.org

Information on this title: www.cambridge.org/9780521815369

© Cambridge University Press 2003

This book is in copyright. Subject to statutory exception and to the provision of relevant collective licensing agreements, no reproduction of any part may take place without the written permission of Cambridge University Press.

First published in print format 2003

```

ISBN-13 978-0-511-07668-8 eBook (EBL)

ISBN-10 0-511-07668-1 eBook (EBL)

ISBN-13 978-0-521-81536-9 hardback

ISBN-10 0-521-81536-3 hardback

ISBN-13 978-0-521-89351-0 paperback

ISBN-10 0-521-89351-8 paperback

```

Cambridge University Press has no responsibility for the persistence or accuracy of URLs for external or third-party internet websites referred to in this book, and does not guarantee that any content on such websites is, or will remain, accurate or appropriate.

## **Contents**

|   | List of figures                                    | page xi |

|---|----------------------------------------------------|---------|

|   | List of tables                                     | XV      |

|   | About the authors                                  | xvi     |

|   | To the Reader                                      | xvii    |

|   | Acknowledgments                                    | xviii   |

|   | Introduction                                       | xix     |

| 1 | Equipment familiarization: multimeter, breadboard, |         |

|   | and oscilloscope                                   | 1       |

|   | 1.1 Multimeter                                     | 1       |

|   | 1.2 Breadboard                                     | 2       |

|   | 1.2.1 Measuring voltage                            | 4       |

|   | 1.2.2 Measuring current; resistance and Ohm's law  | 5       |

|   | 1.2.3 Measuring resistance                         | 8       |

|   | 1.3 Oscilloscope                                   | 8       |

|   | 1.3.1 Probes and probe test                        | 10      |

|   | 1.3.2 Display                                      | 11      |

|   | 1.3.3 Vertical controls                            | 11      |

|   | 1.3.4 Horizontal sweep                             | 12      |

|   | 1.3.5 Triggering                                   | 12      |

|   | 1.3.6 Additional features                          | 13      |

| 2 | RC circuits                                        | 15      |

|   | 2.1 Review of capacitors                           | 15      |

|   | 2.1.1 Use of capacitors; review of AC circuits     | 17      |

|   | 2.1.2 Types and values of capacitors               | 19      |

|   |                                                    |         |

|   | 2.2 Review of current, voltage, and power                | 20 |

|---|----------------------------------------------------------|----|

|   | 2.2.1 Destructive demonstration of resistor power rating | 21 |

|   | 2.3 Potentiometer as voltage divider                     | 22 |

|   | 2.3.1 DC voltage divider                                 | 23 |

|   | 2.3.2 AC voltage divider                                 | 23 |

|   | 2.4 RC circuit                                           | 24 |

|   | 2.5 RC circuit as integrator                             | 24 |

|   | 2.6 Low-pass filter                                      | 25 |

|   | 2.7 RC circuit as differentiator                         | 27 |

|   | 2.8 High-pass filter                                     | 28 |

|   | 2.9 Summary of high- and low-pass filters                | 28 |

| 3 | Diodes                                                   | 31 |

|   | 3.1 Semiconductor basics                                 | 31 |

|   | 3.2 Types of diodes                                      | 35 |

|   | 3.3 Rectification                                        | 36 |

|   | 3.4 Diode action – a more sophisticated view             | 37 |

|   | 3.5 Measuring the diode characteristic                   | 38 |

|   | 3.6 Exploring rectification                              | 40 |

|   | 3.7 Input and output impedance                           | 45 |

| 1 | Bipolar transistors                                      | 47 |

|   | 4.1 Bipolar-junction-transistor basics                   | 47 |

|   | 4.1.1 Basic definitions                                  | 50 |

|   | 4.1.2 Simplest way to analyze transistor circuits        | 51 |

|   | 4.1.3 Ebers–Moll transistor model                        | 52 |

|   | 4.2 Experiments                                          | 54 |

|   | 4.2.1 Checking transistors with a meter                  | 54 |

|   | 4.2.2 Emitter follower                                   | 55 |

|   | 4.2.3 Common-emitter amplifier                           | 57 |

|   | 4.2.4 Collector as current source                        | 59 |

|   | 4.2.5 Transistor switch                                  | 60 |

|   | 4.3 Additional exercises                                 | 61 |

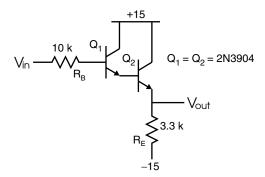

|   | 4.3.1 Darlington connection                              | 61 |

|   |                                                          | 01 |

| vii | Contents |

|-----|----------|

|     |          |

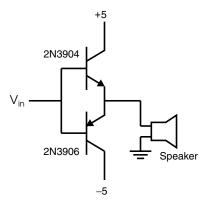

|   | 4.3.2 Push–pull driver                                 | 62 |

|---|--------------------------------------------------------|----|

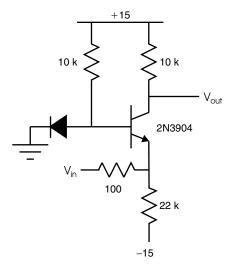

|   | 4.3.3 Common-base amplifier                            | 63 |

| 5 | Transistors II: FETs                                   | 65 |

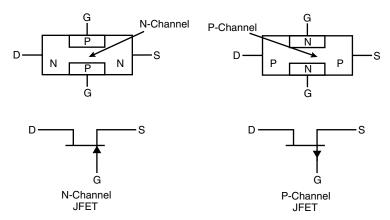

|   | 5.1 Field-effect transistors                           | 65 |

|   | 5.1.1 FET characteristics                              | 66 |

|   | 5.1.2 Modeling FET action                              | 68 |

|   | 5.2 Exercises                                          | 69 |

|   | 5.2.1 FET characteristics                              | 69 |

|   | 5.2.2 FET current source                               | 70 |

|   | 5.2.3 Source follower                                  | 71 |

|   | 5.2.4 JFET amplifier                                   | 73 |

| 6 | Transistors III: differential amplifier                | 75 |

|   | 6.1 Differential amplifier                             | 75 |

|   | 6.1.1 Operating principle                              | 76 |

|   | 6.1.2 Expected differential gain                       | 76 |

|   | 6.1.3 Measuring the differential gain                  | 77 |

|   | 6.1.4 Input offset voltage                             | 78 |

|   | 6.1.5 Common-mode gain                                 | 78 |

|   | 6.2 Op amps and their building blocks                  | 79 |

|   | 6.2.1 Current mirror                                   | 79 |

|   | 6.2.2 Differential amplifier with current-source loads | 80 |

|   | 6.2.3 Improved current mirror                          | 82 |

|   | 6.2.4 Wilson current mirror                            | 82 |

| 7 | Introduction to operational amplifiers                 | 85 |

|   | 7.1 The 741 operational amplifier                      | 85 |

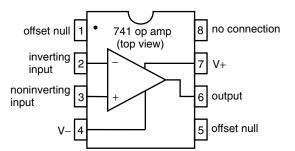

|   | 7.1.1 741 pinout and power connections                 | 86 |

|   | 7.1.2 An ideal op amp                                  | 87 |

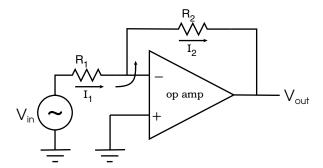

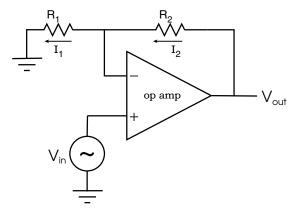

|   | 7.1.3 Gain of inverting and noninverting amplifiers    | 88 |

|   | 7.1.4 Op amp 'golden rules'                            | 90 |

|   | 7.1.5 The nonideal op amp                              | 90 |

| viii | Contents                                                 |     |

|------|----------------------------------------------------------|-----|

|      | 7.2 Experiments                                          | 91  |

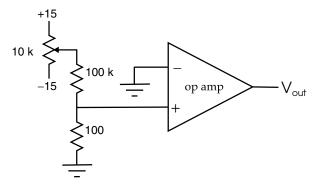

|      | 7.2.1 Testing open-loop gain                             | 91  |

|      | 7.2.2 Inverting amplifier                                | 92  |

|      | 7.2.3 Noninverting amplifier                             | 93  |

|      | 7.2.4 Voltage follower                                   | 94  |

|      | 7.2.5 Difference amplifier                               | 95  |

|      | 7.3 Additional experiments                               | 97  |

|      | 7.3.1 Current source                                     | 97  |

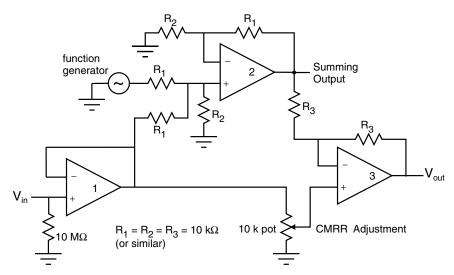

|      | 7.3.2 Noninverting summing amp with difference amplifier | 98  |

| 8    | More op amp applications                                 | 101 |

|      | 8.1 Op amp signal processing                             | 101 |

|      | 8.1.1 Differentiator                                     | 102 |

|      | 8.1.2 Integrator                                         | 103 |

|      | 8.1.3 Logarithmic and exponential amplifiers             | 105 |

|      | 8.2 Experiments                                          | 106 |

|      | 8.2.1 Differential and integral amplifiers               | 106 |

|      | 8.2.2 Logarithmic and exponential amplifiers             | 108 |

|      | 8.2.3 Op amp active rectifier                            | 108 |

|      | 8.2.4 Op amp with push–pull power driver                 | 109 |

|      | 8.3 Additional exercises                                 | 111 |

| 9    | Comparators and oscillators                              | 113 |

|      | 9.1 Experiments                                          | 113 |

|      | 9.1.1 Op amp as comparator                               | 113 |

|      | 9.1.2 Unintentional feedback: oscillation                | 115 |

|      | 9.1.3 Intentional positive feedback: Schmitt trigger     | 116 |

|      | 9.1.4 <i>RC</i> relaxation oscillator                    | 117 |

|      | 9.1.5 555 timer IC                                       | 118 |

|      | 9.2 Additional experiments                               | 121 |

|      | 9.2.1 Alarm!                                             | 121 |

|      | 9.2.2 Sine/cosine oscillator                             | 122 |

|      | 9.2.3 Active bandpass filter                             | 123 |

| 10 | Combinational logic                                   | 125 |

|----|-------------------------------------------------------|-----|

|    | 10.1 Digital logic basics                             | 125 |

|    | 10.1.1 Logic levels                                   | 126 |

|    | 10.1.2 Logic families and history                     | 127 |

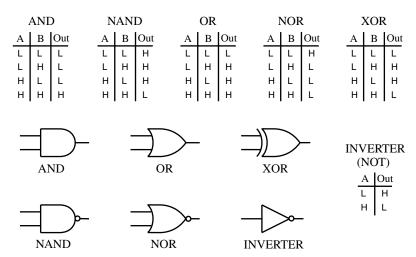

|    | 10.1.3 Logic gates                                    | 129 |

|    | 10.1.4 Summary of Boolean algebra                     | 130 |

|    | 10.2 CMOS and TTL compared                            | 131 |

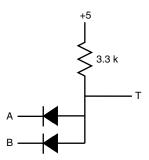

|    | 10.2.1 Diode logic                                    | 131 |

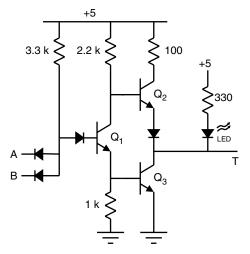

|    | 10.2.2 Transistor–transistor logic (TTL)              | 132 |

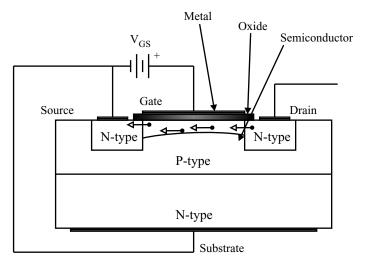

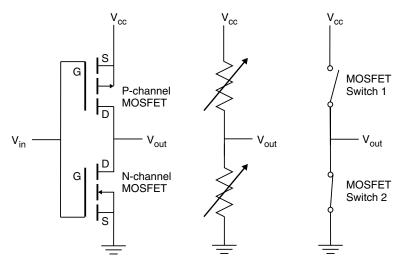

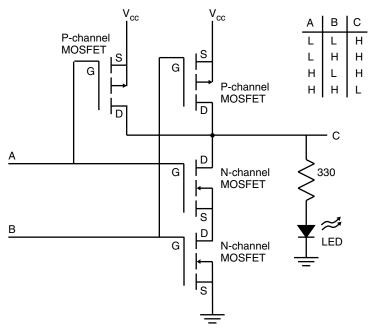

|    | 10.2.3 Complementary MOSFET logic (CMOS)              | 133 |

|    | 10.2.4 Powering TTL and TTL-compatible integrated     |     |

|    | circuits                                              | 136 |

|    | 10.3 Experiments                                      | 137 |

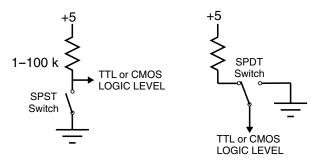

|    | 10.3.1 LED logic indicators and level switches        | 137 |

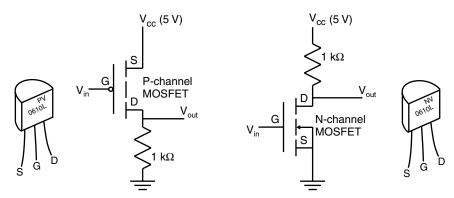

|    | 10.3.2 MOSFETs                                        | 138 |

|    | 10.3.3 CMOS NAND gate                                 | 140 |

|    | 10.3.4 Using NANDs to implement other logic functions | 140 |

|    | 10.3.5 TTL quad XOR gate                              | 141 |

|    | 10.4 Additional exercises                             | 142 |

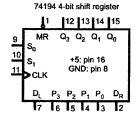

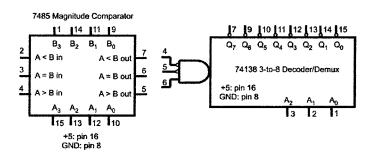

|    | 10.4.1 7485 4-bit magnitude comparator                | 142 |

| 11 | Flip-flops: saving a logic state                      | 143 |

|    | 11.1 General comments                                 | 144 |

|    | 11.1.1 Schematics                                     | 144 |

|    | 11.1.2 Breadboard layout                              | 144 |

|    | 11.1.3 Synchronous logic                              | 144 |

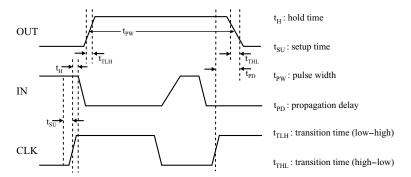

|    | 11.1.4 Timing diagrams                                | 144 |

|    | 11.2 Flip-flop basics                                 | 145 |

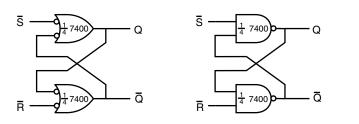

|    | 11.2.1 Simple RS latch                                | 145 |

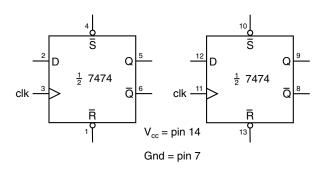

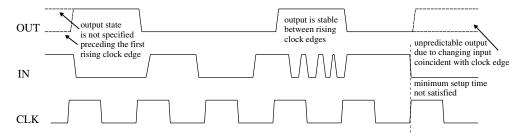

|    | 11.2.2 D-type flip-flop                               | 147 |

|    | 11.3 JK flip-flop                                     | 148 |

|    | 11.4 Tri-state outputs                                | 149 |

|    | A                                                     |     |

| X | Contents |

|---|----------|

|   |          |

|    | 11.5 Flip-flop applications                                | 151  |

|----|------------------------------------------------------------|------|

|    | 11.5.1 Divide-by-four from JK flip-flops                   | 151  |

|    | 11.5.2 Contact bounce                                      | 152  |

|    | 11.5.3 Electronic coin toss                                | 153  |

| 12 | Monostables, counters, multiplexers, and RAM               | 155  |

|    | 12.1 Multivibrators                                        | 156  |

|    | 12.2 Counters                                              | 156  |

|    | 12.3 Experiments                                           | 157  |

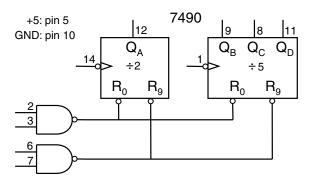

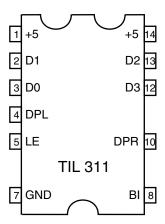

|    | 12.3.1 Bi-quinary ripple counter                           | 157  |

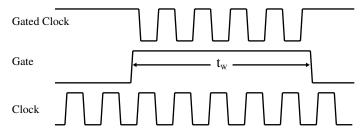

|    | 12.3.2 Monostable multivibrator                            | 159  |

|    | 12.3.3 Multiplexer and finite-state machine                | 162  |

|    | 12.3.4 RAM                                                 | 162  |

| 13 | <br>Digital↔analog conversion                              | 167  |

|    | 13.1 A simple D/A converter fabricated from familiar chips | 168  |

|    | 13.2 Tracking ADC                                          | 170  |

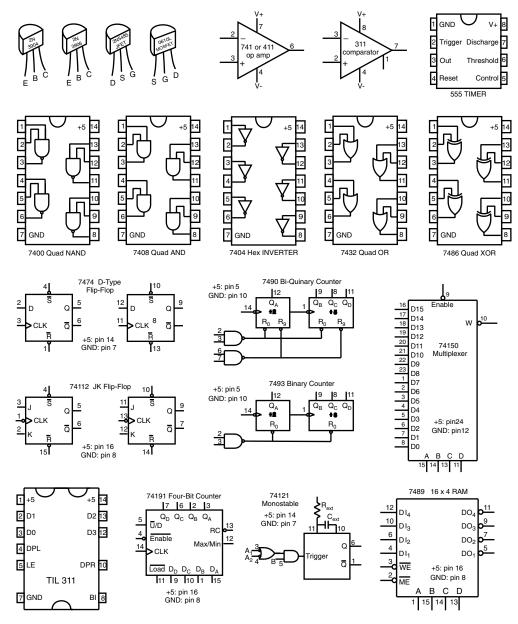

|    | 13.3 080x ADC and DAC chips                                | 171  |

|    | 13.3.1 Successive-approximation ADC                        | 171  |

|    | 13.4 Additional exercises                                  | 177  |

|    | 13.4.1 Digital recording                                   | 177  |

|    | 13.4.2 Successive-approximation ADC built from             | 4.50 |

|    | components                                                 | 178  |

|    | Further reading                                            | 183  |

|    | Appendix A Equipment and supplies                          | 185  |

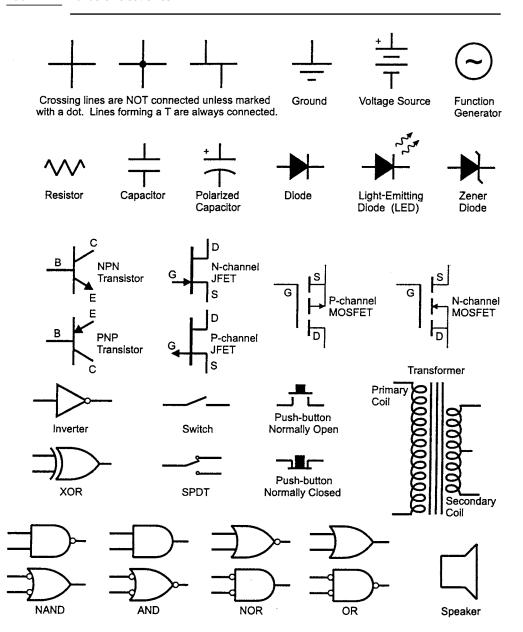

|    | Appendix B Common abbreviations and circuit symbols        | 188  |

|    | Appendix C RC circuits: frequency-domain analysis          | 191  |

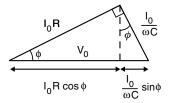

|    | Appendix D Pinouts                                         | 194  |

|    | Glossary of basic electrical and electronic terms          | 197  |

|    | Index                                                      | 199  |

## **Figures**

| 1.1  | Illustration showing many of the basic features of the               |        |

|------|----------------------------------------------------------------------|--------|

|      | PB-503 powered Protoboard.                                           | page 3 |

| 1.2  | Measuring voltage.                                                   | 5      |

| 1.3  | Measuring current.                                                   | 5      |

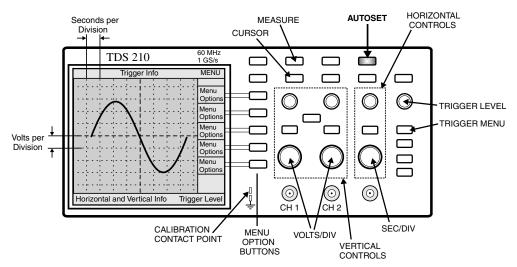

| 1.4  | Illustration of the Tektronix TDS 210 digital oscilloscope.          | 9      |

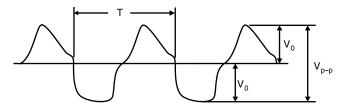

| 2.1  | Representation of an arbitrary, periodic waveform.                   | 18     |

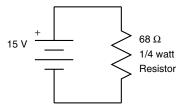

| 2.2  | Circuit demonstrating destructive power loading.                     | 21     |

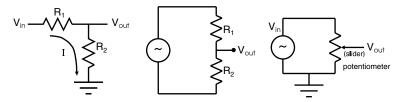

| 2.3  | Three schematics representing a resistive voltage divider.           | 22     |

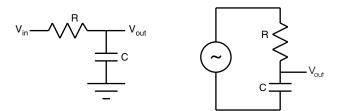

| 2.4  | The voltage-divider concept for RC circuits.                         | 24     |

| 2.5  | High-pass filter or voltage differentiator.                          | 27     |

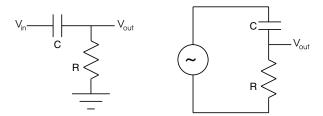

| 2.6  | Relationships among input voltages and capacitor and                 |        |

|      | resistor voltages for high- and low-pass RC filters.                 | 29     |

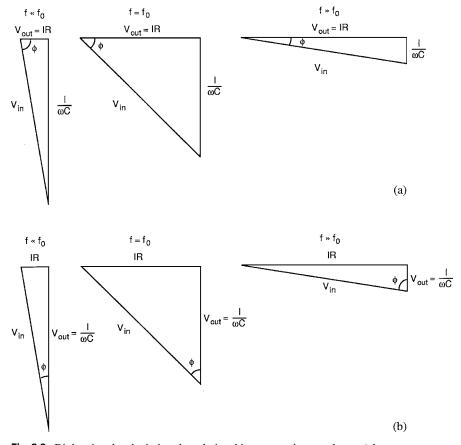

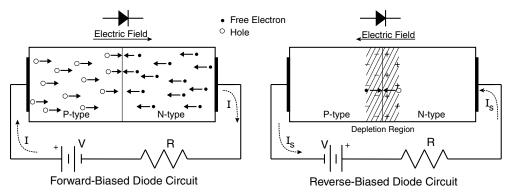

| 3.1  | Representation of a junction between P-type and N-type               |        |

|      | semiconductor material.                                              | 33     |

| 3.2  | Diode circuit symbol and biasing.                                    | 33     |

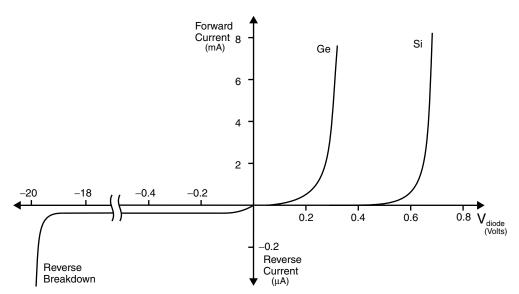

| 3.3  | Typical current-voltage characteristics for germanium                |        |

|      | and silicon diodes.                                                  | 34     |

| 3.4  | Representation of physical diodes and symbols used in                |        |

|      | circuit diagrams.                                                    | 35     |

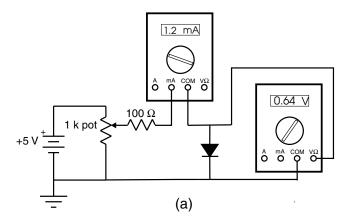

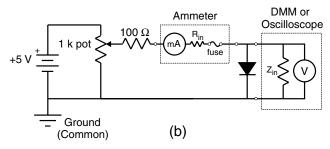

| 3.5  | Measuring the forward characteristic of a diode.                     | 39     |

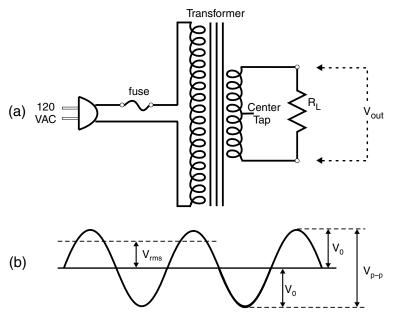

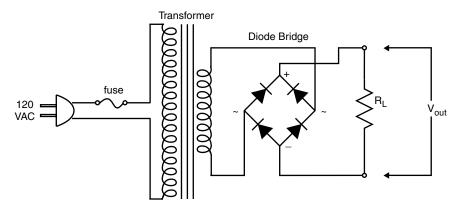

| 3.6  | Power transformer supplies $V_{\rm out} \approx 25 \text{ V r.m.s.}$ | 41     |

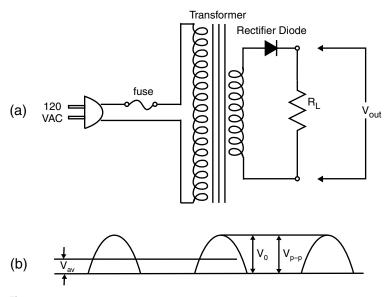

| 3.7  | Power transformer with half-wave rectification.                      | 42     |

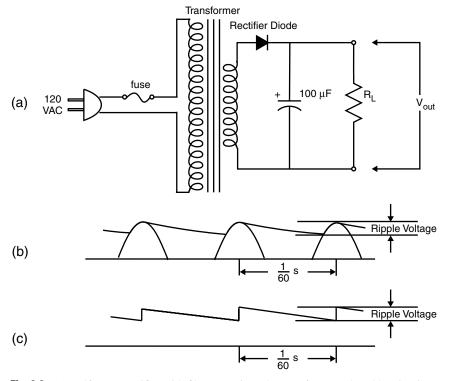

| 3.8  | Half-wave rectifier with filter capacitor.                           | 42     |

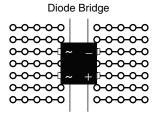

| 3.9  | An example of how to insert a diode bridge into a breadboard.        | 43     |

| 3.10 | Full-wave rectification using diode bridge.                          | 44     |

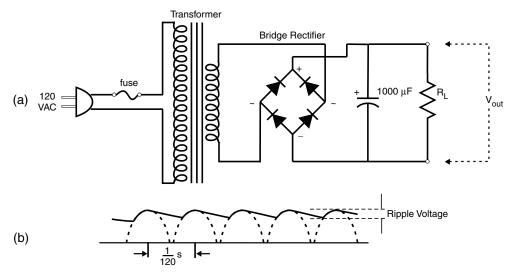

| 3.11 | Full-wave rectification with filter capacitor.                       | 45     |

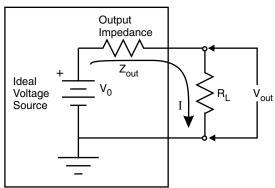

| 3.12 | Complete rectifier circuit.                                          | 46     |

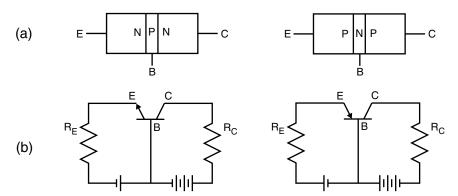

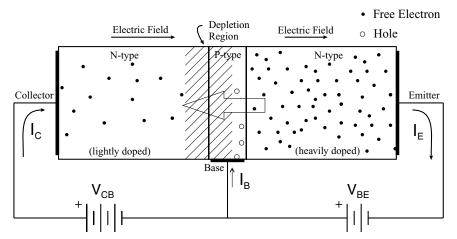

| 4.1  | Construction and circuit symbols and biasing examples for            |        |

|      | NPN and PNP junction transistors.                                    | 48     |

|      |                                                                      |        |

| <u>xii</u> | List of figures                                                |     |

|------------|----------------------------------------------------------------|-----|

| 4.2        | Schematic representation of how an NPN transistor operates.    | 49  |

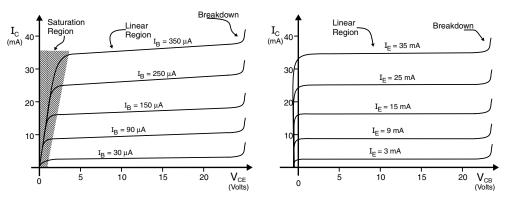

| 4.3        | Characteristic curves for an NPN bipolar transistor.           | 51  |

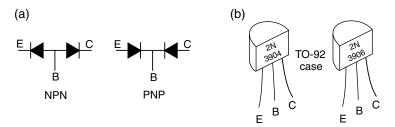

| 4.4        | Transistor as back-to-back diodes; TO-92 pinout.               | 55  |

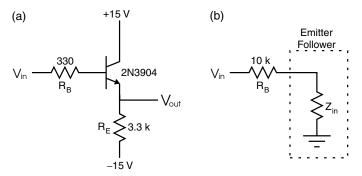

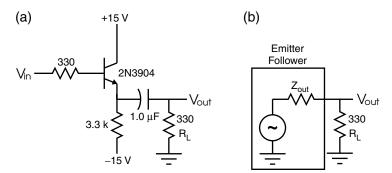

| 4.5        | Emitter follower.                                              | 55  |

| 4.6        | Emitter follower with optional load circuit for measurement    |     |

|            | of $Z_{\text{out}}$ .                                          | 56  |

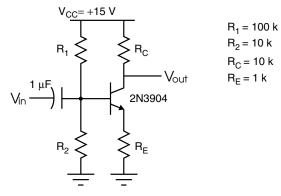

| 4.7        | Common-emitter amplifier.                                      | 57  |

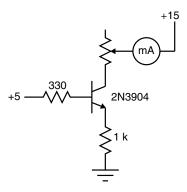

| 4.8        | Transistor current source.                                     | 59  |

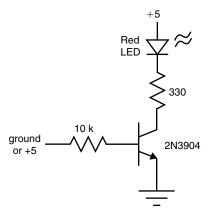

| 4.9        | Transistor switch.                                             | 60  |

| 4.10       | Darlington pair.                                               | 62  |

| 4.11       | Driving loudspeaker with push-pull buffer.                     | 63  |

| 4.12       | Common-base amplifier.                                         | 64  |

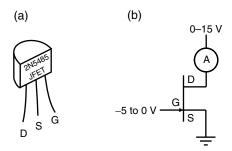

| 5.1        | Construction and circuit symbols of JFETs.                     | 66  |

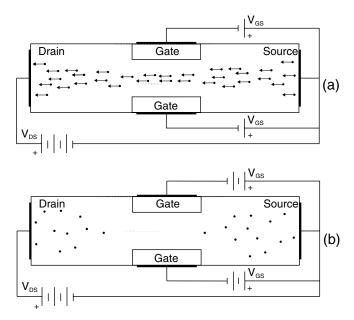

| 5.2        | Schematic representation of JFET operation.                    | 67  |

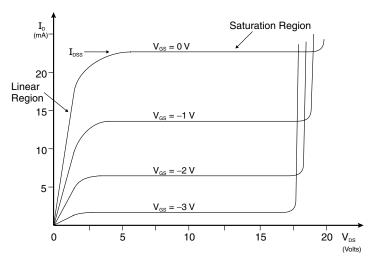

| 5.3        | Idealized common-source characteristic curves for a JFET.      | 67  |

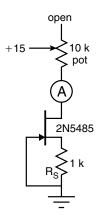

| 5.4        | Circuit for measuring the common-source characteristic curves. | 70  |

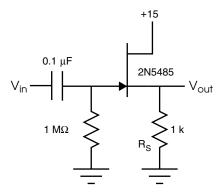

| 5.5        | Self-biasing JFET current source.                              | 71  |

| 5.6        | Source follower.                                               | 72  |

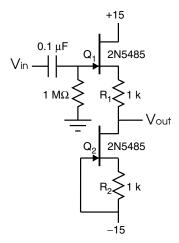

| 5.7        | Source follower with current-source load.                      | 73  |

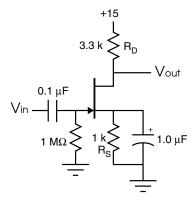

| 5.8        | JFET amplifier.                                                | 73  |

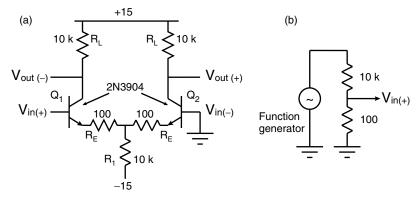

| 6.1        | Differential amplifier and function generator with             |     |

|            | 100-to-1 attenuator.                                           | 76  |

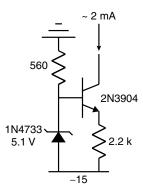

| 6.2        | Current sink for differential amplifier.                       | 79  |

| 6.3        | Current mirror.                                                | 80  |

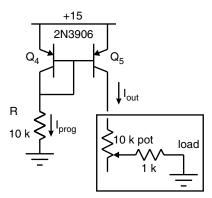

| 6.4        | Differential amplifier with current-mirror load.               | 81  |

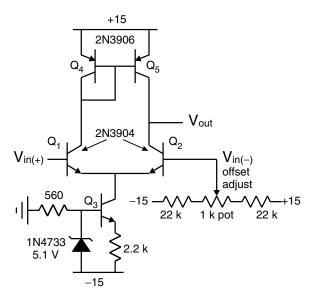

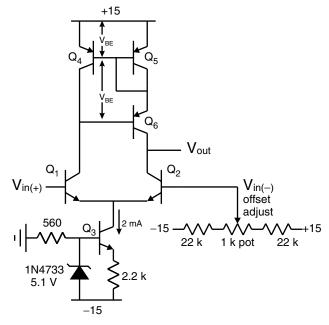

| 6.5        | Differential amplifier with Wilson-current-mirror load.        | 82  |

| 7.1        | Diagram of 8-pin DIP 741 package showing 'pinout'.             | 86  |

| 7.2        | Op amp inverting-amplifier circuit.                            | 88  |

| 7.3        | Op amp noninverting-amplifier circuit.                         | 89  |

| 7.4        | Open-loop op amp test circuit.                                 | 91  |

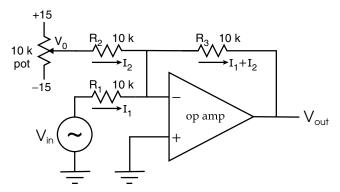

| 7.5        | Circuit for demonstrating summing junction.                    | 93  |

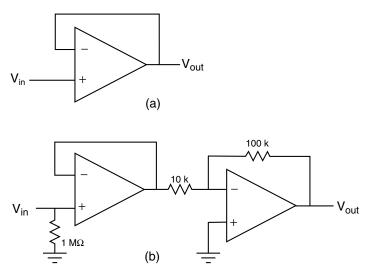

| 7.6        | Op amp voltage follower and voltage follower as the input      |     |

|            | stage to an inverting-op-amp circuit.                          | 95  |

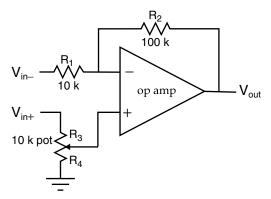

| 7.7        | Difference amplifier.                                          | 96  |

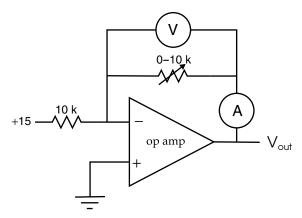

| 7.8        | Op amp current source.                                         | 98  |

| 7.9        | Fancy summing circuit.                                         | 99  |

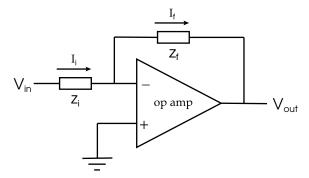

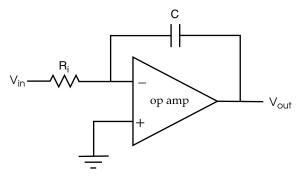

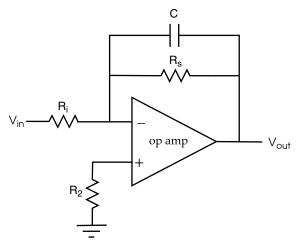

| 8.1        | Generalized op amp inverting-amplifier circuit.                | 102 |

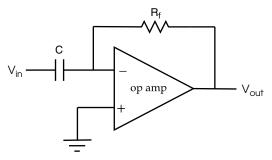

| 8.2   | Basic op amp differentiator.                                       | 102 |

|-------|--------------------------------------------------------------------|-----|

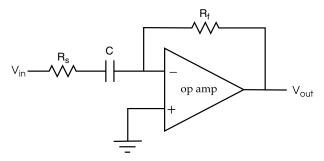

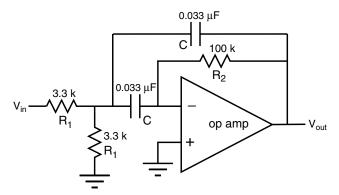

| 8.3   | Improved op amp differentiator.                                    | 103 |

| 8.4   | Basic op amp integrator.                                           | 104 |

| 8.5   | Improved op amp integrator.                                        | 104 |

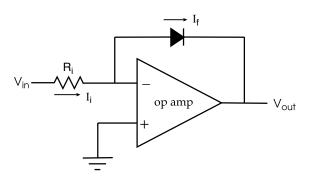

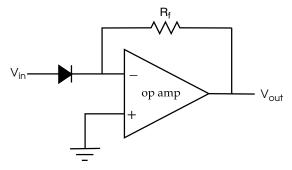

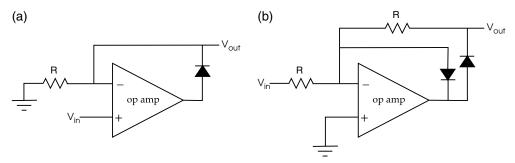

| 8.6   | Op amp logarithmic amplifier.                                      | 105 |

| 8.7   | Op amp exponential amplifier.                                      | 105 |

| 8.8   | Simple and improved versions of an op amp half-wave rectifier.     | 109 |

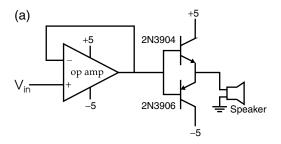

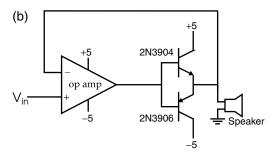

| 8.9   | Op amp follower with push-pull output-buffer power driver          |     |

|       | with two feedback arrangements.                                    | 110 |

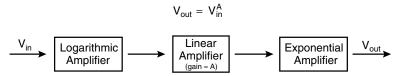

| 8.10  | Block diagram showing how to build an 'exponentiator'.             | 111 |

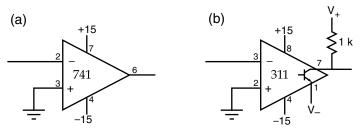

| 9.1   | Poor comparator and 311 comparator.                                | 114 |

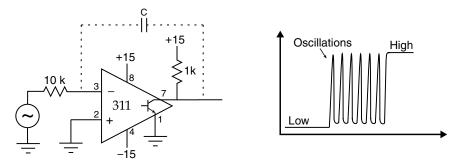

| 9.2   | 311 comparator with 10 k series input resistor.                    | 115 |

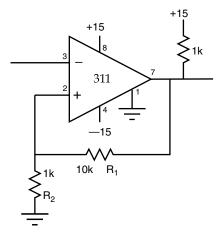

| 9.3   | Schmitt trigger using 311 comparator.                              | 116 |

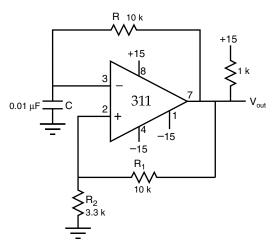

| 9.4   | RC relaxation oscillator using comparator.                         | 118 |

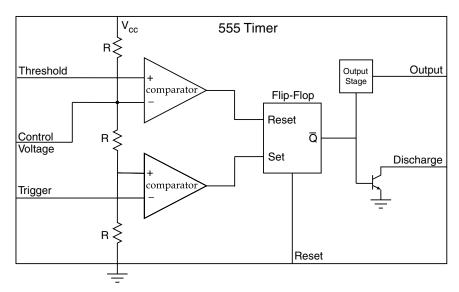

| 9.5   | Block diagram for the 555 timer IC.                                | 119 |

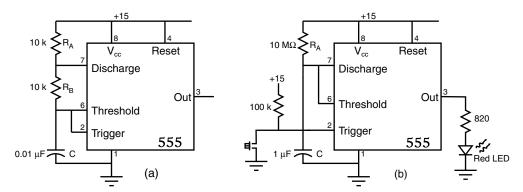

| 9.6   | 555 timer IC used as an oscillator and as a one-shot or timer.     | 120 |

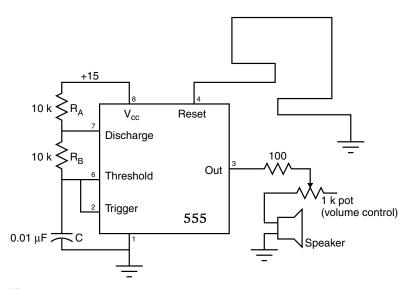

| 9.7   | 555 timer configured as an alarm.                                  | 121 |

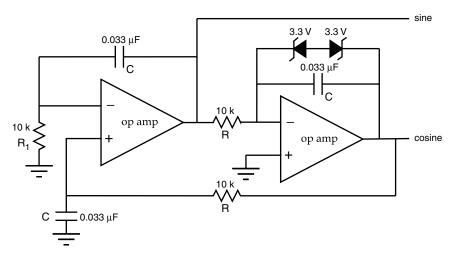

| 9.8   | Sine/cosine oscillator.                                            | 122 |

| 9.9   | Active bandpass filter.                                            | 123 |

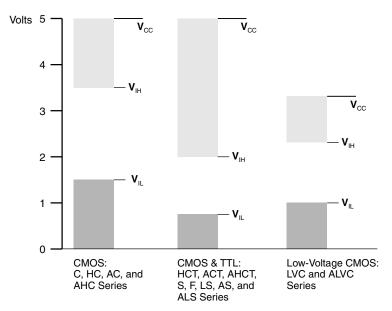

| 10.1  | Logic levels for various 7400-family lines.                        | 127 |

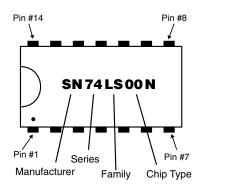

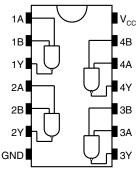

| 10.2  | Labeling of 7400-series chips.                                     | 129 |

| 10.3  | Standard logic gates with truth tables.                            | 130 |

| 10.4  | De Morgan's theorems expressed symbolically.                       | 131 |

| 10.5  | Two-input diode gate.                                              | 132 |

| 10.6  | Diode-transistor NAND gate using 2N3904s.                          | 132 |

| 10.7  | Schematic representation of an 'enhancement-mode'                  |     |

|       | N-channel MOSFET.                                                  | 134 |

| 10.8  | Schematic representations of a CMOS inverter constructed           |     |

|       | using one N-channel and one P-channel MOSFET.                      | 135 |

| 10.9  | Schematic representation of a CMOS NAND gate with LED              |     |

|       | logic-level indicator.                                             | 136 |

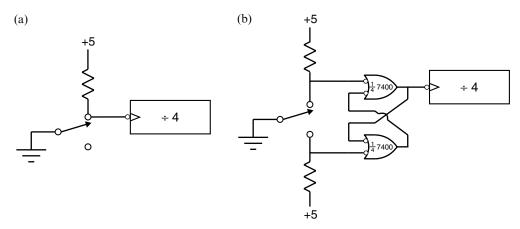

| 10.10 | Logic-level switch using either an SPST or SPDT switch and a       |     |

|       | pull-up resistor.                                                  | 137 |

| 10.11 | Circuits for measuring the channel resistance as a function of     |     |

|       | gate voltage.                                                      | 138 |

| 11.1  | Timing diagram with timing definitions for a rising-edge-triggered |     |

|       | flip-flop.                                                         | 145 |

|       |                                                                    |     |

| xiv  | List of figures                                                    |     |  |  |

|------|--------------------------------------------------------------------|-----|--|--|

| 11.2 | Simple RS latch made of two-input NANDs with state table.          | 146 |  |  |

| 11.3 | 7474 D-type flip-flop with state table.                            | 147 |  |  |

| 11.4 | Sample timing diagram for a (positive-edge-triggered) 7474 D-type  |     |  |  |

|      | flip-flop.                                                         | 147 |  |  |

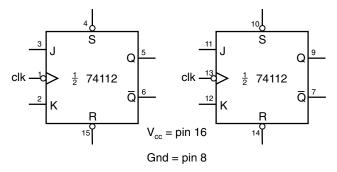

| 11.5 | Pinout of the 74112 JK flip-flop.                                  | 149 |  |  |

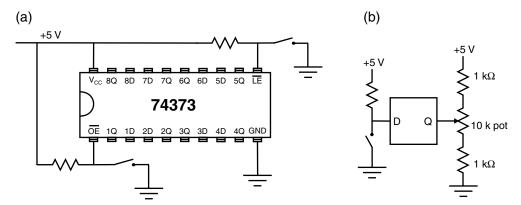

| 11.6 | Pinout and power connections for the 74373 and input and output    |     |  |  |

|      | connections for testing the tri-state output.                      | 150 |  |  |

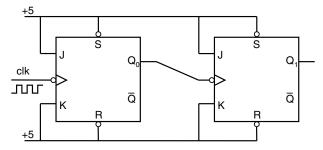

| 11.7 | Divide-by-four ripple counter.                                     | 151 |  |  |

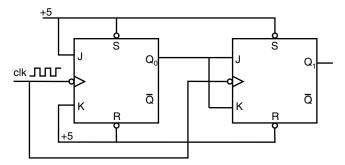

| 11.8 | Synchronous divide-by-four counter.                                | 152 |  |  |

| 11.9 | Looking at contact bounce by driving a divide-by-four counter      |     |  |  |

|      | from a switch.                                                     | 153 |  |  |

| 12.1 | Pinout of 7490 decade counter.                                     | 157 |  |  |

| 12.2 | Pinout of TIL311 hex display.                                      | 158 |  |  |

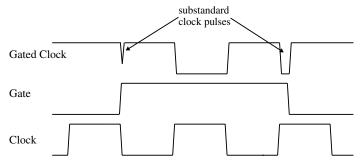

| 12.3 | Timing diagram for a gated clock signal.                           | 160 |  |  |

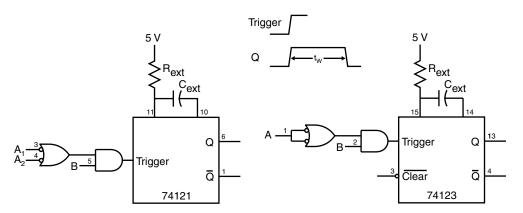

| 12.4 | Pinout of '121 and '123 one-shots with external RC timing network. | 160 |  |  |

| 12.5 | Substandard outputs resulting from gating clock signals.           | 161 |  |  |

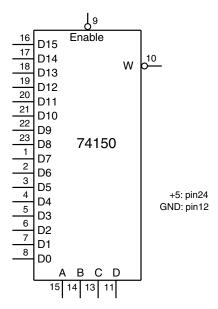

| 12.6 | Pinout of 74150 16-to-1 multiplexer.                               | 163 |  |  |

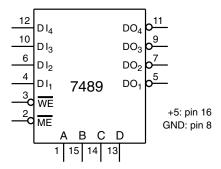

| 12.7 | Pinout of 7489 16×4 RAM.                                           | 163 |  |  |

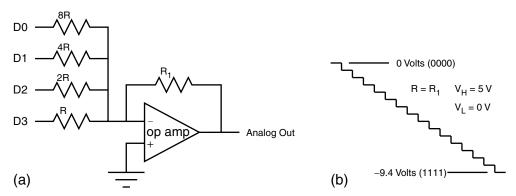

| 13.1 | Simple D/A converter and output waveform resulting from input      |     |  |  |

|      | counting sequence.                                                 | 168 |  |  |

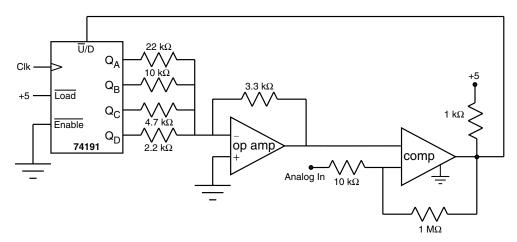

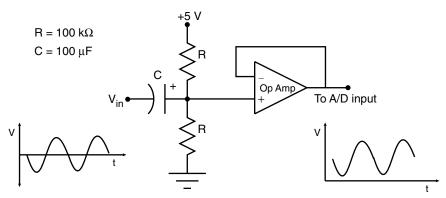

| 13.2 | Simple A/D converter.                                              | 171 |  |  |

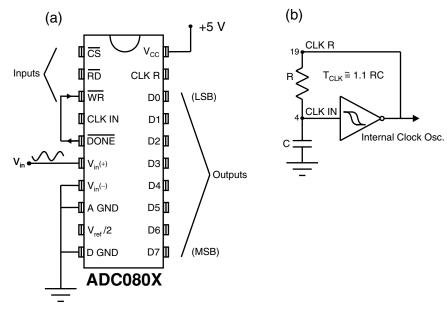

| 13.3 | Pinout for ADC080x series of A/D converters and the on-chip        |     |  |  |

|      | self-clocking configuration.                                       | 172 |  |  |

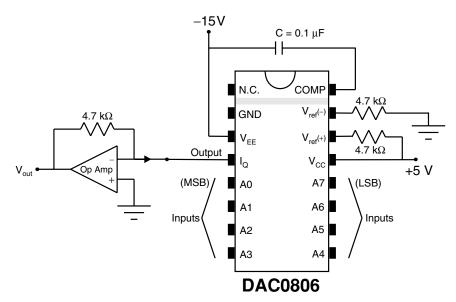

| 13.4 | Pinout for DAC080x series of D/A chips.                            | 175 |  |  |

| 13.5 | Method for producing a DC-shifted waveform.                        | 176 |  |  |

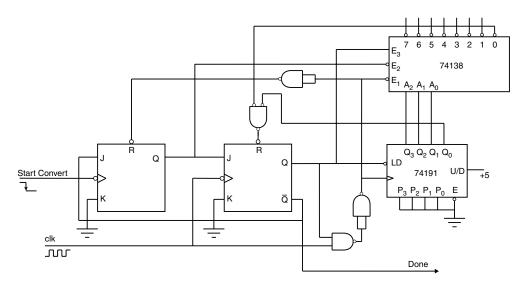

| 13.6 | Control logic for 8-bit successive-approximation ADC.              | 179 |  |  |

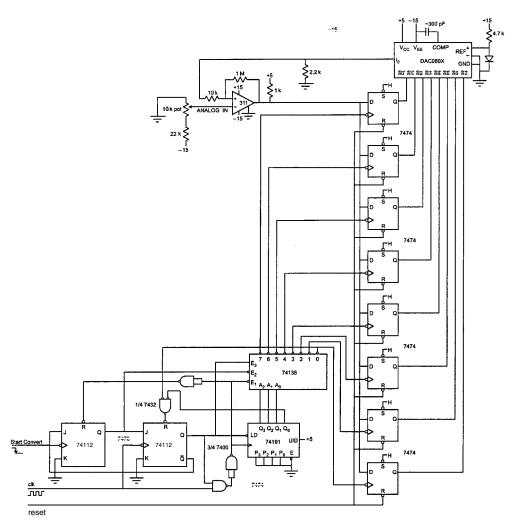

| 13.7 | 8-bit successive-approximation ADC.                                | 180 |  |  |

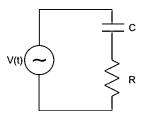

| C.1  | Series RC circuit.                                                 | 193 |  |  |

| C.2  | Right triangle to illustrate Eq. C.17.                             | 193 |  |  |

## **Tables**

| 1.1  | Digital multimeter inputs.                              | page 2 |

|------|---------------------------------------------------------|--------|

| 1.2  | Color code for nonprecision resistors.                  | 7      |

| 2.1  | Some typical dielectric materials used in capacitors.   | 16     |

| 3.1  | A sample of commercially available diodes.              | 36     |

| 4.1  | A sample of commercially available bipolar transistors. | 50     |

| 10.1 | Common families within the 7400 series.                 | 128    |

#### About the authors

Dr Daniel M. Kaplan received his Ph.D. in Physics in 1979 from the State University of New York at Stony Brook. His thesis experiment discovered the b quark, and he has devoted much of his career to experimentation at the Fermi National Accelerator Laboratory on properties of particles containing heavy quarks. He has taught electronics laboratory courses for non-electrical-engineering majors over a fifteen-year period at Northern Illinois University and at Illinois Institute of Technology, where he is currently Professor of Physics and Director of the Center for Accelerator and Particle Physics. He also serves as Principal Investigator of the Illinois Consortium for Accelerator Research. He has been interested in electronics since high school, during the junior year of which he designed a computer based on DTL integrated circuits. Over more than twenty-five years in experimental particle physics he has often been responsible for much of his experiments' custom-built electronic equipment. He is the author or co-author of over 150 scientific papers and one encyclopedia article, and co-editor of three books on heavy-quark physics and related fields.

Dr Christopher G. White is Assistant Professor of Physics at Illinois Institute of Technology. He received his Ph.D. in Physics from the University of Minnesota in 1990. He has authored or co-authored over 100 scientific articles in the field of high-energy particle physics, and his current research interests involve neutrinos and hyperons. Dr White is an enthusiastic and dedicated teacher who enjoys helping students to overcome their fear of electronics and to gain both confidence and competence.

#### To the Reader

Some of you may be encountering electronic circuits and instruments for the first time. Others may have 'played around' with such stuff if, for example, you were ever bitten by the 'ham radio' bug. In either case, this sequence of laboratory experiments has been designed to introduce you to the fundamentals of modern analog and digital electronics.

We use electronic equipment all the time in our work and recreation. Scientists and engineers need to know a bit of electronics, for example to modify or repair some piece of equipment, or to interface two pieces of equipment that may not have been designed for that purpose. To that end, our goal is that by the end of the book, you will be able to design and build any little analog or digital circuit you may find useful, or at least understand it well enough to have an intelligent conversation about the problem with an electrical engineer. A basic knowledge of electronics will also help you to understand and appreciate the quirks and limitations of instruments you will be using in research, testing, development, or process-control settings.

We expect few of you to have much familiarity with such physical theories as electromagnetism or quantum mechanics, so the thrust of this course will be from phenomena and instruments toward theory, not the other way round. If your curiosity is aroused concerning theoretical explanations, so much the better, but unfamiliarity with physical theory should not prevent you from building or using electronic circuits and instruments.

## **Acknowledgments**

We are grateful to Profs Carlo Segre and Tim Morrison for their contributions and assistance, and especially to the IIT students without whom this book would never have been possible. Finally, we thank our wives and children for their support and patience. It is to them that we dedicate this book.

#### Introduction

This book started life as the laboratory manual for the course Physics 300, 'Instrumentation Laboratory', offered every semester at Illinois Institute of Technology to a mix consisting mostly of physics, mechanical engineering, and aeronautical engineering majors. Each experiment can be completed in about four hours (with one or two additional hours of preparation).

This book differs from existing books of its type in that it is faster paced and goes into a bit less depth, in order to accommodate the needs of a one-semester course covering the elements of both analog and digital electronics. In curricula that normally include one year of laboratory instruction in electronics, it may be suitable for the first part of a two-semester sequence, with the second part devoted to computers and computer interfacing – this scheme has the virtue of separating the text for the more rapidly changing computer material from the more stable analog and digital parts.

The book is also suitable for self-study by a person who has access to the necessary equipment and wants a hands-on introduction to the subject. We feel strongly, and experience at IIT has borne out, that to someone who will be working with electronic instrumentation, a hands-on education in the techniques of electronics is much more valuable than a blackboard-and-lecture approach. Certainly it is a better learning process than simply reading a book and working through problems.

The appendices suggest sources for equipment and supplies, provide tables of abbreviations and symbols, and list recommendations for further reading, which includes chapter-by-chapter correspondences to some popular electronics texts written at similar or somewhat deeper levels to ours: the two slim volumes by Dennis Barnaal, *Analog Electronics for Scientific Application* and *Digital Electronics for Scientific Application* (reissued by Waveland Press, 1989); Horowitz and Hill's comprehensive *The Art of Electronics* (Cambridge University Press, 1989); Diefenderfer and Holton's *Principles of Electronic Instrumentation* (Saunders, 1994);

and Simpson's *Introductory Electronics for Scientists and Engineers* (2nd edition, Prentice-Hall, 1987). There is also a glossary of terms and pinout diagrams for transistors and ICs used within. The reader is presumed to be familiar with the rudiments of differential and integral calculus, as well as with elementary college physics (including electricity, magnetism, and direct- and alternating-current circuits, although these topics are reviewed in the text).

The order we have chosen for our subject matter begins with the basics – resistors, Ohm's law, simple AC circuits – then proceeds towards greater complexity by introducing nonlinear devices (diodes), then active devices (bipolar and field-effect transistors). We have chosen to discuss transistors before devices made from them (operational amplifiers, comparators, digital circuitry) so that the student can understand not only how things work but also why.

There are other texts that put integrated circuits, with their greater ease of use, before discrete devices; or digital circuits, with their simpler rules, before the complexities of analog devices. We have tried these approaches on occasion in our teaching and found them wanting. Only by considering first the discrete devices from which integrated circuits are made can the student understand and appreciate the remarkable properties that make ICs so versatile and powerful. A course based on this book thus builds to a pinnacle of intellectual challenge towards the middle, with the three transistor chapters. After the hard uphill slog, it's smooth sailing from there (hold onto your seatbelts!).

The book includes step-by-step instructions and explanations for the following experiments:

- 1. Multimeter, breadboard, and oscilloscope;

- 2. RC circuits;

- 3. Diodes and power supplies;

- 4. Transistors I;

- 5. Transistors II: FETs;

- 6. Transistors III: differential amplifier;

- 7. Introduction to operational amplifiers;

- 8. More op-amp applications;

- 9. Comparators and oscillators;

- 10. Combinational logic;

- 11. Flip-flops: saving a logic state;

- 12. Monostables, counters, multiplexers, and RAM;

- 13. Digital ↔ analog conversion.

These thirteen experiments fit comfortably within a sixteen-week semester. If you or your instructor prefers, one or two experiments may easily be omitted to leave a couple of weeks at the semester's end for independent student projects. To this end, Chapter 6, 'Transistors III', has been designed so that no subsequent experiment depends on it; obviously this is also the case for Chapter 13, 'Digital ↔ analog conversion', which has no subsequent experiment.

As you work through the exercises, you will find focus questions and detailed instructions indicated by the symbol '▷'. Key concepts for each exercise will be denoted by the symbol '•'. Finally, the standard system of units for electronics is the MKS system. Although you may occasionally run across other unit systems, we adhere strictly to the MKS standard.

## Equipment familiarization: multimeter,breadboard, and oscilloscope

In this chapter you will become acquainted with the 'workhorses' of electronics testing and prototyping: multimeters, breadboards, and oscilloscopes. You will find these to be indispensable aids both in learning about and in doing electronics.

#### Apparatus required

One dual-trace oscilloscope, one powered breadboard, one digital multimeter, two 10X attenuating scope probes, red and black banana leads, two alligator clips.

#### 1.1 Multimeter

You are probably already familiar with multimeters. They allow measurement of voltage, current, and resistance. Just as with wristwatches and clocks, in recent years digital meters (commonly abbreviated to DMM for digital multimeter or DVM for digital voltmeter) have superseded the analog meters that were used for the first century and a half or so of electrical work. The multimeters we use have various input jacks that accept 'banana' plugs, and you can connect the meter to the circuit under test using two banana-plug leads. The input jacks are described in Table 1.1. Depending on how you configure the meter and its leads, it displays

- the voltage difference between the two leads,

- the current flowing through the meter from one lead to the other, or

- the resistance connected *between* the leads.

Multimeters usually have a selector knob that allows you to select what is to be measured and to set the full-scale range of the display to handle inputs of various size. Note: to obtain the highest measurement precision, set the knob to the lowest setting for which the input does not cause overflow.

| Input jack | Purpose                                      | Limits <sup>a</sup> |

|------------|----------------------------------------------|---------------------|

| COM        | reference point used for all measurements    |                     |

| $V\Omega$  | input for voltage or resistance measurements | 1000 V DC/750 V AC  |

| mA         | input for current measurements (low scale)   | 200 mA              |

| 10 A       | input for current measurements (high scale)  | 10 A                |

**Table 1.1.** Digital multimeter inputs.

To avoid damaging the meter, be sure to read the safety warnings in its data sheet or instruction booklet.

#### 1.2 Breadboard

'Breadboard' may seem a peculiar term! Its origins go back to the days when electronics hobbyists built their circuits on wooden boards. The breadboards we use represent a great step forward in convenience, since they include not only sockets for plugging in components and connecting them together, but also power supplies, a function generator, switches, logic displays, etc.

The exercises that follow were designed using the Global Specialties PB-503 Protoboard. If you do not have access to a PB-503, any suitable breadboard will do, provided you have a function generator and two variable power supplies. Additional components that you will need along the way (that are built into the PB-503) include a 1 k and a 10 k potentiometer, a small 8  $\Omega$  speaker, two debounced push-button switches, several LED logic indicators, and several on–off switches.

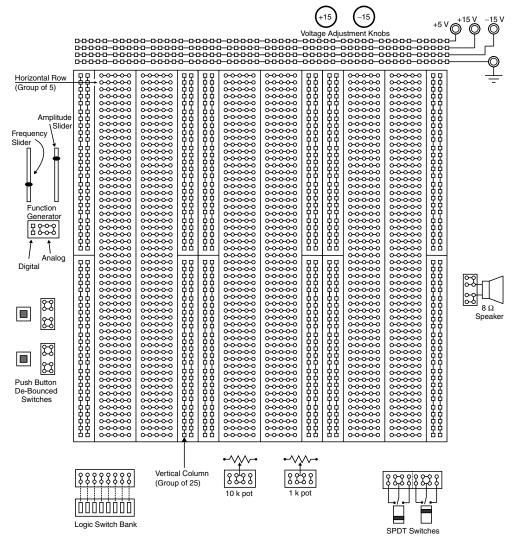

Fig. 1.1 displays many of the basic features of the PB-503. (For simplicity, some PB-503 features that will be used in experiments in later chapters have been omitted.) While the following description is specific to the PB-503, many other breadboards share some, if not all, of these features. The description will thus be of some use for users of other breadboard models as well.

The breadboard's sockets contain spring contacts: if a bare wire is pushed into a socket, the contacts press against it, making an electrical connection. The PB-503's sockets are designed for a maximum wire thickness of 22 AWG ('American Wire Gauge') – anything thicker (i.e., with *smaller*

<sup>&</sup>lt;sup>a</sup>For the BK Model 2703B multimeters used in the authors' labs.

**Fig. 1.1.** Illustration showing many of the basic features of the PB-503 powered Protoboard, with internal connections shown for clarity. Note that each vertical column is broken into halves with no built-in connection between the top and bottom.

AWG number) may damage the socket so that it no longer works reliably for thin wires. The PB-503 sockets are internally connected in groups of five (horizontal rows) or twenty five (vertical columns; see Fig. 1.1).

Each power supply connects to a 'banana' jack and also to a row of sockets running along the top edge of the unit. The three supplies, +5 V (red jack), +15 V (yellow jack), and -15 V (blue jack), have a common

'ground' connection (black jack). The +15 V and -15 V supplies are actually adjustable, using the knobs provided, from less than 5 volts to greater than 15 volts.

#### 1.2.1 Measuring voltage

Voltage is always referenced to something, usually a local ground. For the following exercises you will measure voltage with respect to the breadboard ground, which is also the common ground for the three power supplies. To measure a voltage, you will first connect the 'common' jack of the meter to the breadboard common (i.e., breadboard ground). Next you will connect the meter's 'voltage' jack to the point of interest. The meter will then tell you the voltage with respect to ground at this one point.

When connecting things, it's always a good idea to use color coding to help keep track of which lead is connected to what. Use a black bananaplug lead to connect the 'common' input of the meter to the 'ground' jack of the breadboard (black banana jack labeled with a '\(\psi'\)' or '\(\psi'\)' symbol). Use a red banana-plug lead with the 'V' input of the meter.

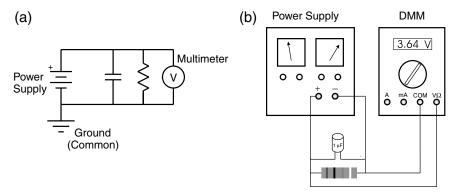

Since the DMM is battery powered, it is said to 'float' with respect to ground (i.e., within reason, one may connect the DMM's common jack to any arbitrary voltage with respect to the breadboard ground). It is therefore possible to measure the voltage drop across any circuit element by simply connecting the DMM directly across that element (see Fig. 1.2).

#### Warning: This is not true for most AC-powered meters and oscilloscopes.

- ▶ To practice measuring voltages, measure and record the voltage between each power supply jack and ground. In each case set the meter's range for the highest precision (i.e., one setting above overflow).

- Adjust the +15 V and −15 V supplies over their full range and record the minimum and maximum voltage for each. Carefully set the +15 V supply to a voltage half-way between its minimum and maximum for use in the next part.

<sup>&</sup>lt;sup>1</sup> If you wonder what we mean by 'within reason', ask yourself what bad thing would happen if you connected the DMM common to, say, twenty million volts – if you're interested, see e.g. H. C. Ohanian, *Physics*, 2nd edition, vol. 2, 'Interlude VI' (Norton, New York, 1988), esp. pp. VI–8 for more information on this.

**Fig. 1.2.** Measuring voltage. (a) An arbitrary circuit diagram is shown as an illustration of how to use a voltmeter. Note that the meter measures the voltage drop across both the resistor and capacitor (which have identical voltage drops since they are connected in parallel). (b) A drawing of the same circuit showing how the leads for a DMM should be connected when measuring voltage. Notice how the meter is connected in parallel with the resistor.

**Fig. 1.3.** Measuring current. (a) Schematic diagram of series circuit consisting of power supply, 10 k potentiometer, and multimeter. (Note that the center tap of the potentiometer is left unconnected in this exercise – accidentally connecting it to power or ground could lead to excessive current flow and burn out the pot.) (b) A drawing of the same circuit showing how the DMM leads should be configured to measure current. Note that the meter is connected in series with the resistor.

#### 1.2.2 Measuring current; resistance and Ohm's law

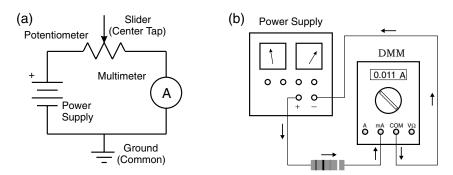

Current is measured by connecting a current meter (an ammeter, or a DMM in its 'current' mode) in series with the circuit element through which the current flows (see Fig. 1.3). Note carefully the differences between Fig. 1.2 and Fig. 1.3.

Recall that Ohm's law relates current I, voltage V, and resistance R according to

$$V = IR. (1.1)$$

This is not a universal law of electrical conduction so much as a statement that there exist certain materials for which current is linearly proportional to voltage.<sup>2</sup> Materials with such a linear relationship are used to fabricate 'resistors': objects with a known and stable resistance. Usually they are little cylinders of carbon, carbon film, metal film, or wound-up wire, encased in an insulating coating, with wire leads sticking out the ends. Often the resistance is indicated by means of colored stripes according to the resistor color code (Table 1.2). Resistors come in various sizes according to their power rating. The common sizes are  $\frac{1}{8}$  W,  $\frac{1}{4}$  W,  $\frac{1}{2}$  W, 1 W, and 2 W.

You can easily verify this linear relationship between voltage and current using the fixed  $10~k\Omega$  (10~000~ohm) resistance provided between the two ends of one of the breadboard's 'potentiometers'. A potentiometer is a type of resistor that has an adjustable 'center tap' or 'slider', allowing electrical connections to be made not only at the two ends, but also at an adjustable point along the resistive material.

The '10 k pot' (as it is called for short) is located near the bottom edge of the breadboard, and can be adjusted by means of a large black knob.<sup>3</sup> Inside the breadboard's case, the ends of the pot (as well as the center tap) connect to sockets as labeled on the breadboard's front panel. By pushing wires into the sockets you can make a series circuit (Fig. 1.3) consisting of an adjustable power supply, the 10 k pot, and the multimeter (configured to measure current). You can attach alligator clips to the meter leads to connect them to the wires. **But**, before doing so, be sure to observe the following warnings:

- First, turn off the breadboard power to avoid burning anything out if you happen to make a mistake in hooking up the circuit.

- Be careful to keep any exposed bits of metal from touching each other and making a 'short circuit'! Note that most of the exposed metal on

Of course, the existence of other materials (namely semiconductors) for which the *I-V* relationship is *non*linear makes electronics much more interesting and underlies the transformation of daily life brought about by electronics during the twentieth century.

<sup>&</sup>lt;sup>3</sup> If you don't have a PB-503 breadboard, find a 10 k pot on your breadboard if it has one; otherwise you will have to purchase a separate 10 k pot.

**Table 1.2.** Color code for nonprecision resistors (5, 10, or 20% tolerance).

The resistance in ohms is the sum of the values in columns 1 and 2, multiplied by the value in column 3, plus or minus the tolerance in column 4. For example, the color code for a 1 k resistor would be 'brown-black-red', for 51  $\Omega$  'green-brown-black', for 330  $\Omega$  'orange-orange-brown', etc.

| Stripe: | 1        | 2               | 3        | 4 (tolerance) |

|---------|----------|-----------------|----------|---------------|

| Black   | 0        | 0               | $10^{0}$ |               |

| Brown   | 10       | 1               | $10^{1}$ |               |

| Red     | 20       | 2               | $10^{2}$ |               |

| Orange  | 30       | 3               | $10^{3}$ |               |

| Yellow  | 40       | 4               | $10^{4}$ |               |

| Green   | 50       | 5               | $10^{5}$ |               |

| Blue    | 60       | 6               | $10^{6}$ |               |

| Violet  | 70       | 7               | $10^{7}$ |               |

| Gray    | 80       | 8               | $10^{8}$ |               |

| White   | 90       | 9               | $10^{9}$ |               |

| Gold    |          |                 |          | 5%            |

| Silver  |          |                 |          | 10%           |

| None    |          |                 |          | 20%           |

| _       | Stripe 1 | tripe 2<br>Stri | pe 3     |               |

|         |          |                 | Toleran  | ce Stripe     |

the breadboard (screw heads for example) has a low-resistance path to ground.

- If you accidentally connect power or ground to the potentiometer's center tap, you can easily burn out the pot, rendering it useless! If in doubt, have someone check your circuit before turning on the power.

- ▶ Use Ohm's law to predict the current that will flow around the circuit if you use the power supply that you set to its midpoint in the previous exercise. What current should flow if the supply is set to its minimum voltage? What is the current if the supply is set to its maximum voltage?

Now turn on the breadboard power, measure the currents for these three voltages, and compare with your predictions. Make a graph of voltage vs. current from these measurements. Is the relationship linear? How close is the slope of voltage vs. current to  $10 \text{ k}\Omega$ ?

#### 1.2.3 Measuring resistance

Now turn off the breadboard power and disconnect your series circuit. In this and the following part, the pot should connect only to the meter.

- $\triangleright$  Set the meter for resistance and measure and record the resistance between the two ends of your 10 k pot. Due to manufacturing tolerances, you will probably find that it is not exactly 10 kΩ. By what percentage does it differ from the nominal 10 kΩ value? Does the measured value agree more closely with the slope you previously measured than with the nominal value? Explain.

- Now connect the meter between the center tap and one end of the pot. What resistance do you observe? What happens to the resistance as you turn the potentiometer's knob?

- ▶ Leaving the knob in one place, measure and record the resistance between the center tap and each end. Do the two measurements add up to the total you measured above? They should – explain why.

#### 1.3 Oscilloscope

With its many switches and knobs, a modern oscilloscope can easily intimidate the faint of heart, yet the scope is an essential tool for electronics troubleshooting and you must become familiar with it. Accordingly, the rest of this laboratory session will be devoted to becoming acquainted with such an instrument and seeing some of the things it can do.

The oscilloscope we use is the Tektronix TDS210 (illustrated in Fig. 1.4). If you don't have a TDS210, any dual-trace oscilloscope, analog or digital, can be used for these labs as long as the bandwidth is high enough – ideally, 30 MHz or higher. While the description below may not correspond exactly to your scope, with careful study of its manual you should be able to figure out how to use your scope to carry out these exercises.

The TDS210 is not entirely as it appears. In the past you may have used an oscilloscope that displayed voltage as a function of time on a

**Fig. 1.4.** Illustration of the Tektronix TDS210 digital oscilloscope. The basic features to be used in this tutorial are marked. Note and remember the location of the 'AUTOSET' button – when all else fails, try autoset!

cathode-ray tube (CRT). While the TDS210 can perform a similar function, it does not contain a CRT (part of the reason it is so light and compact).

Until the 1990s, most oscilloscopes were purely 'analog' devices: an input voltage passed through an amplifier and was applied to the deflection plates of a CRT to control the position of the electron beam. The position of the beam was thus a direct analog of the input voltage. In the past few years, analog scopes have been largely superseded by digital devices such as the TDS210 (although low-end analog scopes are still in common use for TV repair, etc.).

A digital scope operates on the same principle as a digital music recorder. In a digital scope, the input signal is sampled, digitized, and stored in memory. The digitized signal can then be displayed on a computer screen.

One of your first objectives will be to set up the scope to do some of the things for which you may already have used simpler scopes. After that, you can learn about multiple traces and triggering. In order to have something to look at on the scope, you can use your breadboard's built-in function generator, a device capable of producing square waves, sinusoidal waves, and triangular waves of adjustable amplitude and frequency. But start by using the built-in 'calibrator' signal provided by the scope on a metal contact labeled 'probe comp' (or something similar), often located near the lower right-hand corner of the display screen.

Note that a leg folds down from the bottom of the scope near the front face. This adjusts the viewing angle for greater comfort when you are seated at a workbench, so we recommend that you use it.

#### 1.3.1 Probes and probe test

Oscilloscopes come with *probes*: cables that have a coaxial connector (similar to that used for cable TV) on one end, for connecting to the scope, and a special tip on the other, for connecting to any desired point in the circuit to be tested. To increase the scope's input impedance and affect the circuit under test as little as possible, we generally use a '10X' attenuating probe, which has circuitry inside that divides the signal voltage by ten. Some scopes sense the nature of the probe and automatically correct for this factor of ten; others (such as the TDS210) need to be told by the user what attenuation setting is in use.

As mentioned above, your scope should also have a built-in 'calibrator' circuit that puts out a standard square wave you can use to test the probe (see Fig. 1.4). The probe's coaxial connector slips over the 'CH 1' or 'CH 2' input jack and turns clockwise to lock into place. The probe tip has a spring-loaded sheath that slides back, allowing you to grab the calibrator-signal contact with a metal hook or 'grabber'.

An attenuating scope probe can distort a signal. The manufacturer therefore provides a 'compensation adjustment' screw, which needs to be tuned for minimum distortion. The screw is usually located on the assembly that connects the probe to the scope, or, occasionally, on the tip assembly.

- ▶ Display the calibrator square-wave signal on the scope. If the signal looks distorted (i.e., not square), carefully adjust the probe compensation using a small screwdriver. (If you have trouble achieving a stable display, try 'AUTOSET'.)

- ▷ Check your other probe. Make sure that both probes work, are properly compensated, and have equal calibrations. Sketch the observed waveform.

(Consult your oscilloscope user manual for more information about carrying out a probe test.)

Note that each probe also has an alligator clip (sometimes referred to as the 'reference lead' or 'ground clip'). This connects to the shield of the coaxial cable. It is useful for reducing noise when looking at high-frequency

(time intervals of order nanoseconds) or low-voltage signals. Since it is connected directly to the scope's case, which is grounded via the third prong of the AC power plug, it must never be allowed to touch a point in a circuit other than ground! Otherwise you will create a short circuit by connecting multiple points to ground, which could damage circuit components.

This is no trouble if you are measuring a voltage with respect to ground. But if you want to measure a voltage drop between two points in a circuit, neither of which is at ground, first observe one point (with the probe) and then the other. The difference between the two measurements is the voltage across the element. During this process, the reference lead should remain firmly attached to ground and should not be moved! (Alternatively, you can use two probes and configure the scope to subtract one input from the other.)

Warning: A short circuit will occur if the probe's reference lead is connected anywhere other than ground.

#### 1.3.2 Display

Your oscilloscope user's manual will explain the information displayed on the scope's screen. Record the various settings: timebase calibration, vertical scale factors, etc.

Explain briefly the various pieces of information displayed around the edges of the screen.

The following exercises will give you practice in understanding the various settings. For each, you should study the description in your oscilloscope user's manual. The description below is specific to the TDS210; if you have a different model, your manual will explain the corresponding settings for your scope.

#### 1.3.3 Vertical controls

There is a set of 'vertical' controls for each channel (see Fig. 1.4). These adjust the sensitivity (volts per vertical division on the screen) and offset (the vertical position on the screen that corresponds to zero volts). The 'CH 1' and 'CH 2' menu buttons can be used to turn the display of each

channel on or off; they also select which control settings are programmed by the push-buttons just to the right of the screen.

▶ Display a waveform from the calibrator on channel 1. What happens when you adjust the POSITION knob? The VOLTS/DIV knob?

#### 1.3.4 Horizontal sweep

To the right of the vertical controls are the horizontal controls (see Fig. 1.4). Normally, the scope displays voltage on the vertical axis and time on the horizontal axis. The SEC/DIV knob sets the sensitivity of the horizontal axis, i.e. the interval of time per horizontal division on the screen. The POSITION knob moves the image horizontally on the screen.

- ▶ How many periods of the square wave are you displaying on the screen? How many divisions are there per period? What time interval corresponds to a horizontal division? Explain how these observations are consistent with the known period of the calibrator signal.

- ▶ Adjust the SEC/DIV knob to display a larger number of periods. Now what is the time per division? How many divisions are there per period?

#### 1.3.5 Triggering

Triggering is probably the most complicated function performed by the scope. To create a stable image of a repetitive waveform, the scope must 'trigger' its display at a particular voltage, known as the trigger 'threshold'. The display is synchronized whenever the input signal crosses that voltage, so that many images of the signal occurring one after another can be superimposed in the same place on the screen. The LEVEL knob sets the threshold voltage for triggering.

You can select whether triggering occurs when the threshold voltage is crossed from below ('rising-edge' triggering) or from above ('falling-edge' triggering) using the trigger menu (or, for some scope models, using trigger control knobs and switches). You can also select the signal source for the triggering circuitry to be channel 1, channel 2, an external trigger signal, or the 120 V AC power line, and control various other triggering features as well.

Since setting up the trigger can be tricky, the TDS210 provides an automatic setup feature (via the AUTOSET button) which can lock in on

almost any repetitive signal presented at the input and adjust the voltage sensitivity and offset, the time sensitivity, and the triggering to produce a stable display.

▶ After getting a stable display of the calibrator signal, adjust the LEVEL knob in each direction until the scope just barely stops triggering. What is the range of trigger level that gives stable triggering on the calibrator signal? How does it compare with the amplitude of the calibrator waveform? Does this make sense? Explain.

Next connect the scope probe to the breadboard's function generator – you can do this by inserting a wire into the appropriate breadboard socket and grabbing the other end of the wire with the scope probe's grabber. The function generator's amplitude and frequency are adjusted by means of sliders and slide switches.

- ▶ Look at each of the waveforms available from the function generator: square, sine, and triangle. Try out the frequency and voltage controls and explain how they work. Adjust the function generator's frequency to about 1 kHz.

- ▷ Display both scope channels, with one channel looking at the output of the function generator and the other looking at the scope's calibrator signal. Make sure the vertical sensitivity and offset are adjusted for each channel so that the signal trace is visible.

- ▶ What do you see on the screen if you trigger on channel 1? On channel 2?

- ▶ What do you see if neither channel causes triggering (for example, if the trigger threshold is set too high or too low)?

- ▶ How does this depend on whether you select 'normal' or 'auto' trigger mode? Why? (If you find this confusing, be sure to ask for help, or study the oscilloscope manual more carefully.)

#### 1.3.6 Additional features

The TDS210 has many more features than the ones we've described so far. Particularly useful are the digital measurement features. Push the MEASURE button to program these. You can use them to measure the amplitude, period, and frequency of a signal. The scope does not measure amplitude directly. How then can you derive the amplitude from something the scope does measure?

▶ Using the measurement features, determine the amplitude, frequency, and period of a waveform of your choice from the function generator.

You can also use the on-screen cursors to make measurements.

- ▶ Use the cursors to measure the half-period of the signal you just measured.

- Explain how you made these measurements and what your results were. (A feature that comes in particularly useful on occasion is signal averaging; this is programmed via the ACQUIRE button and allows noise, which tends to be random in time, to be suppressed relative to signal, which is usually periodic.)

# 2 RC circuits

Capacitors are not useful in DC circuits since they contain insulating gaps, which are open circuits for DC. However, for voltages that change with time, a simple series circuit with a capacitor and a resistor can output the time derivative or integral of an input signal, or can filter out low-frequency or high-frequency components of a signal. But before plunging into the world of time-varying voltage and current (i.e., *alternating-current* circuits), we explore the *voltage-divider* idea using direct current, since it gives us a simple way to understand circuits containing more than one component in series. Then we apply it to the analysis of *RC* circuits as filters. Note that the series *RC* circuit can be analyzed in two different ways:

- via the exponential charging/discharging equation, and

- as an AC voltage divider.

Both approaches are valid – in fact, they are mathematically equivalent – but the first is more useful when using capacitors as integrators or differentiators, whereas the second is more useful when analyzing low-pass and high-pass filters. The first is referred to as the *time-domain* approach, since it considers the voltage across the capacitor as a function of time, and the second as the *frequency-domain* approach, since it focuses on the filter attenuation *vs.* frequency.

## Apparatus required

Oscilloscope, digital multimeter, breadboard, 68  $\Omega$  and 10 k $\Omega$  resistors, 0.01  $\mu F$  ceramic capacitor.

# 2.1 Review of capacitors

As you may recall from an introductory physics course, a capacitor consists of two parallel conductors separated by an insulating gap. The capacitance,

| Material     | Dielectric constant (κ) |  |  |

|--------------|-------------------------|--|--|

| Vacuum       | 1.0                     |  |  |

| Air (at STP) | 1.00054                 |  |  |

| Paper        | 3.5                     |  |  |

| Mica         | 5.4                     |  |  |

| Ceramic      | ≈100                    |  |  |

|              |                         |  |  |

**Table 2.1.** Some typical dielectric materials used in capacitors.

C, is proportional to the area of the conductors, A, and inversely proportional to their separation, s, multiplied by the *dielectric constant*,  $\kappa$ , of the insulating material:

$$C = \kappa \epsilon_0 A/s$$

,

where, in the MKS system of units, A is in meters squared, s in meters, and C in farads, abbreviated F (1 farad  $\equiv$  1 coulomb per volt). (The constant of proportionality is the so-called *permittivity of free space* and has the value  $\epsilon_0 = 8.854 \times 10^{-12} \text{ F/m}$ ).

The farad is an impractically large unit: for a conductor area of  $1~\rm cm^2$  and separation of  $1~\rm mm$ , with dielectric constant of order 1, the capacitance is  $\sim$  picofarads. To achieve the substantially larger capacitances (of order microfarads) often found in electronic circuits, manufacturers wind ribbon-shaped capacitors up into small cylinders and use insulators of high dielectric strength, such as ceramics or (in the so-called *electrolytic* capacitors) special dielectric pastes, that chemically form an extremely thin insulating layer when a voltage is applied. Table 2.1 gives dielectric constants for some typical dielectrics used in capacitors.

Capacitors thus come in a variety of types, categorized according to the type of dielectric used, which determines how much capacitance can be squeezed into a small volume. Electrolytic and tantalum capacitors are *polarized*, which means that they have a positive end and a negative end, and the applied voltage should be more positive at the positive end than at the negative end – if you reverse-voltage a polarized capacitor it can burn out, or even explode! Paper, mica, and ceramic capacitors are unpolarized and can be hooked up in either direction. The large dielectric constants of the polarized dielectrics permit high capacitance values – up to millifarads in a several-cubic-centimeter can.

#### 2.1.1 Use of capacitors; review of AC circuits

The fundamental rule governing the behavior of capacitors is

$$Q = CV, (2.1)$$

where Q is the charge stored on the capacitor at a given time, V is the voltage across the capacitor at that time, and C is the capacitance. Current can flow into or out of a capacitor, but only to the extent that the charge on the capacitor is changing. In other words, the current into or out of a capacitor is equal to the time derivative of the charge stored on it. You can see the resemblance between Eq. 2.1 and Ohm's law (Eq. 1.1). The key difference is that, for a resistor, it is the *time derivative* of the charge that is proportional to voltage, whereas for a capacitor it is the charge itself.

Capacitors are thus useful only in circuits in which voltages or currents are changing in time, namely AC circuits. We will consider the response of circuits to periodic waveforms; these can be characterized by their frequency, f, and period, T, which of course are related by

$$T = 1/f$$

,

as well as their angular frequency  $\omega = 2\pi f$ . (If f is expressed in hertz  $\equiv$  cycles per second, then T is in seconds and  $\omega$  is in radians per second.) A periodic waveform is also characterized by its *amplitude*, which, assuming the wave is pure AC (i.e. symmetric with respect to ground), is the maximum voltage that it reaches.

There are an infinite variety of AC waveforms, but to understand how capacitors are used, it is sufficient to focus on two: square waves and sine waves. You have already encountered a square wave in the previous chapter – the scope's calibrator signal. A square wave of amplitude  $V_0$  is a signal that oscillates back and forth between two voltage levels, one at  $+V_0$  and one at  $-V_0$ , spending 50% of the time at each level. Note that the peak-to-peak voltage is twice the amplitude:

$$V_{p-p}=2A$$

.

A sine wave is a particularly important case because, by Fourier decomposition, any periodic waveform can be represented as a sum of sine waves of various amplitudes and frequencies. Most of AC circuit analysis therefore concerns itself with the response of circuits to sine waves.

**Fig. 2.1.** Representation of an arbitrary, periodic waveform with period T, amplitude  $V_0$  and peak-to-peak voltage  $V_{\rm p-p}$ .

A sine wave can be represented mathematically by

$$V(t) = V_0 \sin(\omega t + \phi). \tag{2.2}$$

If t is in seconds, this describes a voltage with amplitude  $V_0$  changing sinusoidally in time at the rate of  $\omega$  radians per second. The phase  $\phi$  determines the voltage at t=0:

$$V(0) = V_0 \sin \phi. \tag{2.3}$$

Now suppose such a voltage signal is applied to a capacitor; for simplicity, we choose  $\phi = 0$ , i.e. at t = 0 the voltage is zero. Since we are assuming there is no resistance in the circuit, there is no possibility of a voltage drop anywhere in the circuit. Thus, at any moment in time, the voltage across the capacitor must equal the voltage out of the signal source. To find the resulting current we can differentiate Eq. 2.1:

$$I = \frac{\mathrm{d}Q}{\mathrm{d}t} \tag{2.4}$$

$$=C\frac{\mathrm{d}V}{\mathrm{d}t}\tag{2.5}$$

$$= C\frac{\mathrm{d}}{\mathrm{d}t}(V_0\sin\omega t) \tag{2.6}$$

$$= \omega C V_0 \cos \omega t \tag{2.7}$$

$$= \omega C V_0 \sin(\omega t + 90^\circ). \tag{2.8}$$

We see that the current is also a sine wave, but shifted in time with a phase shift of  $90^{\circ}$ , i.e. the current *leads* the voltage by  $90^{\circ}$ .

We can write an 'Ohm's-law equivalent' for a capacitor, as long as it is understood that we are talking about sinusoidal waveforms only:

$$V_0 = I_0 X_C, (2.9)$$

<sup>&</sup>lt;sup>1</sup> Of course, this is only an idealized approximation, since in any real circuit there is at least the resistance of the wires, and in practice any signal source has some internal resistance.

where  $I_0$  is the amplitude of the current sine wave and  $X_C \equiv 1/\omega C$  is the capacitive reactance of the capacitor. The reactance is thus the effective resistance of the capacitor. Note that it is frequency-dependent, in keeping with our intuition that for DC a capacitor should look like an open circuit (infinite resistance), while at high frequency it should approach a short circuit (zero resistance).

For completeness, we mention here the inductive reactance  $X_L \equiv \omega L$ , where L is the *inductance* of an inductor. Inductors are coils of wire and satisfy the equation

$$V = L \frac{\mathrm{d}I}{\mathrm{d}t}.\tag{2.10}$$

Just as capacitors often employ a dielectric, inductors are often wound on a ferrite core to increase their inductance. Note that the inductor equation relates the voltage across an inductor to the *derivative* of the current through it, while the capacitor equation (Eq. 2.1) relates the voltage across a capacitor to the *integral* of the current. Thus, where the current through a capacitor *leads* the voltage across it, the current through an inductor *lags* the voltage across it by 90°. With respect to its function in a circuit, an inductor can thus be thought of as the opposite of a capacitor. Whereas capacitors are relatively small, light, cheap, and have negligible resistance, inductors tend to be large, heavy, expensive, and have appreciable resistance. Nevertheless, they find important use in filtering applications, e.g. bandpass filters, crossover circuits for hi-fi speakers, radio-frequency circuits, and so forth. In the interests of time we omit inductor exercises from our course, but if you understand capacitors you will have very little difficulty in applying inductors.

#### 2.1.2 Types and values of capacitors

For some reason the various manufacturers' conventions for marking capacitors are particularly confusing – probably it has to do with the fact that many small-value capacitors are physically too small to permit much printing on them. Some common sense is required. Keep in mind that 1 farad is a huge unit! Most capacitors are in the picofarad and microfarad ranges, and these are the two commonly used units. A physically large capacitor that says '10M' on it is usually 10 microfarads, *not* 10 millifarads (for some reason, most manufacturers don't want to print Greek letters, so they use 'M' instead of ' $\mu$ '). A 10 millifarad cap would be labeled '10000M'. A small capacitor that says just '10' on it is 10 picofarads. The other important number is the maximum operating voltage, which is usually printed on the capacitor if there is room.

Some small capacitors are labeled like resistors, either with a color code or with numbers that mean the same thing. The first digit of this capacitance code is the tens, the second is the ones, the third is the power of 10, and the units are picofarads. This is sometimes ambiguous – for example, a capacitor that says '470' could be 470 pF or  $47 \times 10^0 = 47$  pF! Usually the clue is the presence of a letter, following the capacitance code, that indicates the tolerance – J for  $\pm 5\%$ , K for  $\pm 10\%$ , M for  $\pm 20\%$ , etc. – so that '470 K' means 47 pF  $\pm 10\%$ , whereas just 470 means 470 pF! Note that there is no ambiguity if it says 471 – since normal capacitors are not manufactured with enough precision to warrant a third significant digit, the '1' must be the power of ten. When in doubt, you can always check it out by putting it in an *RC* circuit with a known *R* value and measuring the time constant (see below), or by plugging it into a capacitance meter, if you have one.

#### 2.2 Review of current, voltage, and power

Before we get started on *RC* circuits, let us briefly review power dissipation and component ratings – you need to understand these to avoid damaging components.

Voltage is related to potential-energy difference. The voltage drop across any circuit element is directly proportional to the change in energy of a charge as it traverses the circuit element. Specifically,

1 volt = 1 joule/coulomb.

The potential energy (with respect to some reference point) is equal to the voltage multiplied by the charge.

Current refers to the motion of charges. The current through a given surface (e.g. the cross-section of a wire) is defined as the net charge passing through that surface per unit time. The unit for current is the ampere:

1 ampere = 1 coulomb/second.

The product of voltage and current has units of joules/second, otherwise known as watts.

If the voltage drop across a circuit element equals the change in potential energy per unit charge, and the current equals the amount of charge

moving through the element per unit time, then their product equals the power released within the device! The power dissipated within any device is given by

$$P = IV. (2.11)$$

For resistive elements (or when an effective resistance can be defined), Eq. 2.11 can be combined with Ohm's law to give:

$$P = IV = I^2 R = V^2 / R. (2.12)$$

Resistors, diodes, transistors, relays, integrated-circuit chips, etc., are rated (in part) by their maximum allowed power. Exceeding these ratings can have disastrous effects on your circuit, and may even cause a fire! To illustrate this point, our first exercise will deliberately lead to the destruction of a carbon-film resistor.

#### 2.2.1 Destructive demonstration of resistor power rating

Caution: In the following exercise, care must be taken to prevent burns.

The resistor in the following exercise will become **very hot** and may even catch fire (briefly). Keep the body of the resistor well above the breadboard. Do **not** touch the resistor with your fingers. Remove the destroyed resistor using pliers or a similar tool.